## Freescale Semiconductor Technical Data

# Clock Generator for PowerQUICC and PowerPC Microprocessors and Microcontrollers

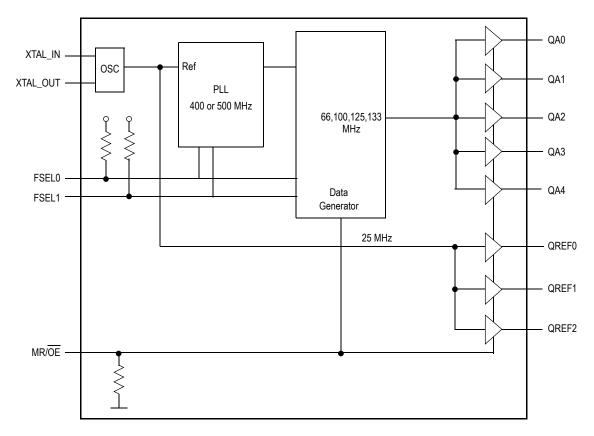

The MPC9819 is a PLL-based clock generator specifically designed for Freescale Microprocessor and Microcontroller applications including the PowerPC and PowerQUICC. This device generates the microprocessor input clock and other microprocessor system and bus clocks at any one of four output frequencies. These frequencies include the popular 66- and 133-MHz PCI/X bus frequencies. The device offers five low-skew clock outputs plus three reference outputs. The clock input reference is 25 MHz and may be derived from an external source or by the addition of a 25-MHz crystal to the on-chip crystal oscillator. The extended temperature range of the MPC9819 supports telecommunication and networking requirements.

#### Features

- 5 LVCMOS outputs for processor and other system circuitry

- 3 Buffered 25-MHz reference clock outputs

- · Crystal oscillator or external reference input

- 25-MHz input reference frequency

- · Selectable output frequencies include: 66, 100, 125, or 133 MHz

- · Low cycle-to-cycle and period jitter

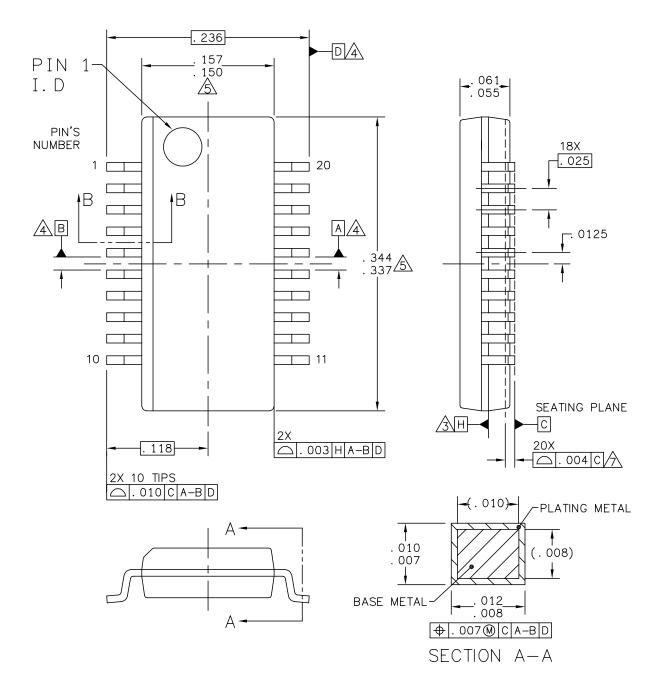

- Package: 20-lead SSOP

- 3.3-V supply

- · Supports computing, networking, and telecommunications applications

- Ambient temperature range: -40°C to +85°C

#### **Functional Description**

SD SUFFIX 20 SSOP PACKAGE CASE 1461-02 EN SUFFIX 20 SSOP PACKAGE Pb-FREE PACKAGE CASE 1461-02

The MPC9819 uses a PLL with a 25-MHz input reference frequency to generate a single bank of five configurable LVCMOS output clocks. The output frequency of this bank is configurable to either 66, 100, 125, or 133 MHz by two FSEL pins. The 25-MHz reference may be either an external frequency source or a 25-MHz crystal. The 25-MHz crystal is directly connected to the XTAL\_IN and XTAL\_OUT pins with no additional components required. An external reference may be applied to the XTAL\_IN pin with the XTAL\_OUT pin left floating. The input reference, whether provided by a crystal or an external input, is also directly buffered to a second bank of three LVCMOS outputs. These outputs may be used as the clock source for processor I/O applications such as an Ethernet PHY.

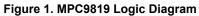

The MPC9819 is packaged in a 20-lead SSOP package.

## Table 1. Pin Configurations

| Pin                     | I/O    | Туре   | Function                                           |

|-------------------------|--------|--------|----------------------------------------------------|

| QA0, QA1, QA2, QA3, QA4 | Output | LVCMOS | Clock Outputs                                      |

| QREF0, QREF1, QREF2     | Output | LVCMOS | Reference Output (25 MHz)                          |

| XTAL_IN                 | Input  | LVCMOS | Crystal Oscillator Input Pin                       |

| XTAL_OUT                | Output | LVCMOS | Crystal Oscillator Output Pin                      |

| FSEL0, FSEL1            | Input  | LVCMOS | Configures Bank A Clock Output Frequency (pull-up) |

| MR/OE                   | Input  | LVCMOS | Enables All Outputs (pull-down)                    |

| V <sub>DD</sub>         | —      | —      | 3.3-V Supply                                       |

| GND                     | —      | —      | Ground                                             |

## Table 2. Function Table

| Control      | Default | 00     | 01      | 10      | 11      |

|--------------|---------|--------|---------|---------|---------|

| FSEL0, FSEL1 | 11      | 66 MHz | 125 MHz | 100 MHz | 133 MHz |

Figure 2. MPC9819 20-Lead SSOP Package Pinout (Top View)

#### **MPC9819 OPERATION**

#### **Crystal Oscillator**

The MPC9819 features a fully integrated Pierce oscillator to minimize system implementation costs. Other than the addition of a 25-MHz crystal, no external components are required. The crystal selection should be: 25 MHz, parallel resonant type with a load specification of  $C_L = 10$  pF. Crystals with a load specification of  $C_L = 20$  pF may be used, however,

the reference frequency may be higher than the specified 25 MHz. Externally supplied capacitors on both the XTAL\_IN and XTAL\_OUT pins may be used to trim the frequency as desired.

The crystal should be located as close to the MPC9819 XTAL\_IN and XTAL\_OUT pins as possible to avoid any board level parasitic.

#### **Table 3. Crystal Specifications**

| Parameter                           | Value              |

|-------------------------------------|--------------------|

| Crystal Cut                         | Fundamental AT Cut |

| Resonance                           | Parallel Resonance |

| Shunt Capacitance (C <sub>O</sub> ) | 5–7 pF             |

| Load Capacitance (C <sub>L</sub> )  | 10 pF              |

| Equivalent Series Resistance (ESR)  | 20–60 Ω            |

#### **Power Supply Bypassing**

The MPC9819 should have all  $V_{DD}$  pins bypassed with 0.01 capacitors and a minimum of one 1.0 capacitor for the overall package. All capacitors should be located as close to the SSOP pins as possible.

#### **External Clock Source**

An external reference source of 25 MHz may be applied to the XTAL\_IN pin. In this mode of operation, the XTAL\_OUT pin should be left floating.

## Table 4. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Characteristics     | Min  | Max | Unit | Condition |

|------------------|---------------------|------|-----|------|-----------|

| V <sub>DD</sub>  | Supply Voltage      | -0.3 | 3.8 | V    |           |

| I <sub>IN</sub>  | DC Input Current    | _    | ±20 | mA   |           |

| I <sub>OUT</sub> | DC Output Current   | _    | ±75 | mA   |           |

| Τ <sub>S</sub>   | Storage Temperature | -65  | 125 | °C   |           |

1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

#### **Table 5. General Specifications**

| Symbol          | Characteristics                          | Min  | Тур                 | Max | Unit | Condition |

|-----------------|------------------------------------------|------|---------------------|-----|------|-----------|

| V <sub>TT</sub> | Output Termination Voltage               | —    | V <sub>DD</sub> ÷ 2 | -   | V    |           |

| MM              | ESD Protection (machine model)           | 200  | _                   | _   | V    |           |

| HBM             | ESD Protection (human body model)        | 2000 | _                   | _   | V    |           |

| LU              | Latch-Up Immunity                        | 200  | —                   | _   | mA   |           |

| C <sub>IN</sub> | Input Capacitance                        | —    | 4                   | _   | pF   | Inputs    |

| C <sub>pd</sub> | Power Dissipation Capacitance            | —    | 8.5                 | _   | pF   |           |

| $\theta_{JA}$   | Thermal Resistance (junction-to-ambient) | —    | 80.8                | _   | °C/W |           |

| Т <sub>С</sub>  | Ambient Temperature                      | -40  |                     | 85  | °C   |           |

## Table 6. DC Characteristics (V\_DD = 3.3 V $\pm$ 5%, T\_A = -40° to +85°C)

| Symbol           | Characteristics                                                                   | Min | Тур      | Max                   | Unit | Condition                                 |

|------------------|-----------------------------------------------------------------------------------|-----|----------|-----------------------|------|-------------------------------------------|

| $V_{\text{IH}}$  | Input High Voltage (XTAL_IN)                                                      | 2.4 | —        | V <sub>DD</sub> + 0.3 | V    | Input threshold = $V_{DD}/2$              |

| V <sub>IH</sub>  | Input High Voltage                                                                | 2.0 | —        | V <sub>DD</sub> + 0.3 | V    |                                           |

| V <sub>IL</sub>  | Input Low Voltage                                                                 | _   | —        | 0.8                   | V    | LVCMOS                                    |

| I <sub>IN</sub>  | Input Current <sup>(1)</sup>                                                      |     | —        | 150                   | μA   | V <sub>IN</sub> = V <sub>DDL</sub> or GND |

| V <sub>OH</sub>  | Output High Voltage                                                               | 2.4 | —        | —                     | V    | I <sub>OH</sub> = -12 mA                  |

| V <sub>OL</sub>  | Output Low Voltage                                                                | _   | —        | 0.4                   | V    | I <sub>OL</sub> = 12 mA                   |

| Z <sub>OUT</sub> | Output Impedance                                                                  | _   | 14       | —                     | Ω    |                                           |

| I <sub>DD</sub>  |                                                                                   | —   | 23<br>32 | 40<br>50              | mA   | 25 MHz reference<br>frequency             |

| IDDBASE          | Base Supply Current <sup>(2)</sup><br>(for dynamic power dissipation calculation) | _   | 14       | —                     | mA   |                                           |

1. Inputs have pull-down resistors affecting the input current. 2.  $P_D = (V_{DD} * I_{DDBASE}) + 5 (V_{DD}^2) * C_{pd} * f_A.$

| Symbol                          | Characteristics                                                                                                                                             | Min | Тур                                 | Max      | Unit                            | Condition                                         |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------|----------|---------------------------------|---------------------------------------------------|

| Input and (                     | Output Timing Specification                                                                                                                                 |     |                                     |          | 1                               |                                                   |

| f <sub>ref</sub>                | Input Reference Frequency 25 MHz Input<br>XTAL Input                                                                                                        |     | 25<br>25                            |          | MHz<br>MHz                      |                                                   |

| f <sub>VCO</sub>                | VCO Frequency Range FSEL0, FSEL1 = 00,01,11<br>FSEL0, FSEL1 = 10                                                                                            |     | 400<br>500                          |          | MHz<br>MHz                      |                                                   |

| f <sub>MCX</sub>                | Output Frequency (QAx)<br>FSEL0, FSEL1 = 00<br>FSEL0, FSEL1 = 10<br>FSEL0, FSEL1 = 10<br>FSEL0, FSEL1 = 01<br>FSEL0, FSEL1 = 11<br>Output Frequency (QREFx) |     | 66.66<br>100<br>125<br>133.33<br>25 |          | MHz<br>MHz<br>MHz<br>MHz<br>MHz | PLL locked                                        |

| f <sub>refPW</sub>              | Reference Input Pulse Width                                                                                                                                 | 10  | —                                   | _        | ns                              | @ 25 MHz                                          |

| DC                              | Output Duty Cycle                                                                                                                                           | 45  | 50                                  | 55       | %                               |                                                   |

| f <sub>out</sub>                | Output Frequency Accuracy Crystal <sup>(3)</sup><br>External Reference                                                                                      |     | —                                   | 100<br>0 | ppm<br>ppm                      | With recommended crystal see Table 3              |

| PLL Speci                       | fications                                                                                                                                                   |     |                                     |          | •                               |                                                   |

| BW                              | PLL Closed Loop Bandwidth <sup>(4)</sup>                                                                                                                    |     | 500                                 |          | kHz                             |                                                   |

| t <sub>LOCK</sub>               | Maximum PLL Lock Time                                                                                                                                       |     |                                     | 10       | ms                              |                                                   |

| Skew and                        | Jitter Specifications                                                                                                                                       |     |                                     |          | •                               |                                                   |

| t <sub>sk(O)</sub>              | Output-to-Output Skew (within a bank)                                                                                                                       |     |                                     | 75       | ps                              |                                                   |

| t <sub>JIT(CC)</sub>            | Cycle-to-Cycle Jitter                                                                                                                                       |     |                                     | 150      | ps                              | @ 25 MHz Input Reference<br>Q <sub>A</sub> output |

| $t_{\rm JIT(PER)}$              | Period Jitter                                                                                                                                               |     |                                     | 100      | ps                              | @ 25 MHz Input Reference<br>Q <sub>A</sub> output |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                                                                                                                       |     |                                     | 1        | ns                              | 20% to 80%                                        |

## Table 7. AC Characteristics<sup>(1)</sup> (2) (V<sub>DD</sub> = $3.3 \text{ V} \pm 5\%$ , T<sub>A</sub> = $-40^{\circ}$ to $+85^{\circ}$ C)

1. AC characteristics are design targets and pending characterization.

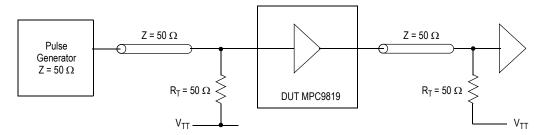

2. AC characteristics apply for parallel output termination of 50  $\Omega$  to V<sub>TT</sub>. 3. Based upon recommended crystal specifications as outlined in operation section.

4. -3 dB point of PLL transfer characteristics.

Figure 3. MPC9819 AC Test Reference (LVCMOS Outputs)

### Table 8. MPC9819 Pin List

| Pin | Description     |

|-----|-----------------|

| 1   | XTAL_IN         |

| 2   | XTAL_OUT        |

| 3   | FSEL0           |

| 4   | V <sub>DD</sub> |

| 5   | FSEL1           |

| 6   | QREF2           |

| 7   | GND             |

| 8   | QREF1           |

| 9   | QREF0           |

| 10  | V <sub>DD</sub> |

| Pin | Description     |

|-----|-----------------|

| 11  | GND             |

| 12  | MR/OE           |

| 13  | QA0             |

| 14  | V <sub>DD</sub> |

| 15  | QA1             |

| 16  | QA2             |

| 17  | GND             |

| 18  | QA3             |

| 19  | QA4             |

| 20  | V <sub>DD</sub> |

#### MPC9819

## PACKAGE DIMENSIONS

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. |  | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--|--------------|------------------|-------------|

| TITLE: 20LD SSOP.                                       |  | DOCUMENT NO  | ): 98ASA10564D   | REV: A      |

| . 15" BODY WIDTH, . O                                   |  | CASE NUMBER  | R: 1461–02       | 20 APR 2005 |

| CASE OUTLINE                                            |  | STANDARD: NO | N-JEDEC          |             |

PAGE 1 OF 3

#### CASE 1461-02 ISSUE A 20 SSOP PACKAGE

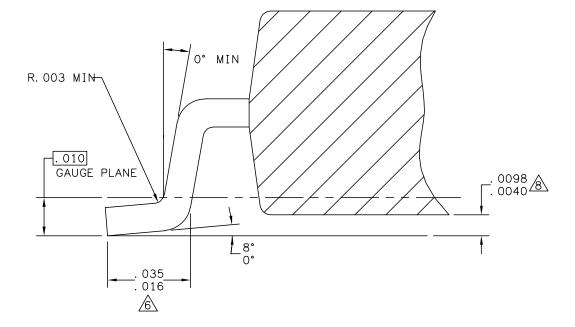

## PACKAGE DIMENSIONS

SECTION B-B

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. |  | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--|--------------|------------------|-------------|

| TITLE: 20LD SSOP,                                       |  | DOCUMENT NO  | ): 98ASA10564D   | REV: A      |

| . 15" BODY WIDTH, . O                                   |  | CASE NUMBER  | 8: 1461-02       | 20 APR 2005 |

| CASE OUTLINE                                            |  | STANDARD: NO | N-JEDEC          |             |

PAGE 2 OF 3

### CASE 1461-02 ISSUE A 20 SSOP PACKAGE

#### MPC9819

NOTES:

- 1. DIMENSIONS ARE IN INCHES.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

$\bigtriangleup$  datum plane h located at mold parting line and coincident with lead, where lead exits plastic body at bottom of parting line.

$\underline{\bigwedge}$  DATUM A, B AND D TO BE DETERMINED WHERE CENTERLINE BETWEEN LEADS EXITS PLASTIC BODY AT DATUM PLANE H.

THIS DIMENSION DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS, BUT DO INCLUDE MOLD MISMATCH AND ARE MEASURED AT THE MOLD PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006 INCHES FOR ENDS AND .008 INCHES FOR SIDES.

6. THIS DIMENSION IS LENGTH OF TERMINAL FOR SOLDERING TO A SUBSTRATE.

$\triangle$  formed leads shall be planar with respect to one another within .004 inches at seating plane.

A THIS DIMENSION IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY.

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. |           | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: 20LD SSOP,                                       |           | DOCUMENT NO  | ): 98ASA10564D   | REV: A      |

| . 15" BODY WIDTH, . O                                   | 25" PITCH | CASE NUMBER  | 8: 1461–02       | 20 APR 2005 |

| CASE OUTLINE                                            |           | STANDARD: NO | N-JEDEC          |             |

PAGE 3 OF 3

#### CASE 1461-02 ISSUE A 20 SSOP PACKAGE

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005. All rights reserved.